# **Optimizing Graph Processing on GPUs**

Wenyong Zhong, Jianhua Sun, Hao Chen, Jun Xiao, Zhiwen Chen, Cheng Chang, and Xuanhua Shi

**Abstract**—Distributed vertex-centric model has been recently proposed for large-scale graph processing. Due to the simple but efficient programming abstraction, similar graph computing frameworks based on GPUs are gaining more and more attention. However, prior works of GPU-based graph processing suffer from load imbalance and irregular memory access because of the inherent characteristics of graph applications. In this paper, we propose a generalized graph computing framework for GPUs to simplify existing models but with higher performance. In particular, two novel algorithmic optimizations, lightweight approximate sorting and data layout transformation, are proposed to tackle the performance issues of current systems. With extensive experimental evaluation under a wide range of real world and synthetic workloads, we show that our system can achieve 1.6x to 4.5x speedups over the state-of-the-art.

Index Terms—GPGPU, Graph Computing, Pregel, Bulk Synchronous Model, Load Imbalance.

# **1** INTRODUCTION

With the rapid development of the Internet, processing very large web graphs has become a hot research issue in both the academia and industry. Large-scale graph processing frameworks are becoming increasingly important for solving problems in scientific computing, data mining, and other domains such as social networks. For example, finding the shortest paths of on-line maps, the citation relationships among twitter forwarding, and the purchasing preference in E-commerce webs, are all typical scenarios that heavily rely on efficient graph computation. However, developing graph processing algorithms over large dataset is challenging in terms of programmability and performance. Thus, a general graph programming framework that provides supports for high performance processing of a wide range of graph algorithms is often desired.

As a result, in the last several years, we have witnessed a growing interest in distributed graph processing, such as Pregel, GraphLab, PowerGraph, GPS, and Mizan, which are purposely-built distributed graph computing systems with easy-to-use programming interfaces and reasonable performance under large-scale workloads. The prominent one is Pregel [24], which was firstly proposed in 2010 as a programming model to address the challenges in parallel computing of large graphs. The high-level programming model of Pregel plays a significant role in abstracting architectural details of parallel computing from programmers. Specifically, the vertex-centric programming model proposed by Pregel greatly relieves the efforts of performing computation on large-scale data-intensive graphs, and provides high expressibility for a wide range of graph algorithms. Similar to MapReduce [13] whose programming model has been

Xuanhua Shi is with School of Computers, Huazhong University of Science and Technology, Wuhan, China. E-mail: {xhshi}@hust.edu.cn adopted successfully in many mainstream parallel environments, the advantages of Pregel have inspired the research of applying the Pregel-like graph computing model to many parallel architectures (e.g. multi-core, GPU, and heterogeneous hybrid systems), such as Grace [27], Medusa [37], and TOTEM [15].

1

With the advancement of GPU hardware and the introduction of GPU programming frameworks such as CUDA [5] and OpenCL [25], GPU has become a more generalized computing device. General purpose computing on GPU (GPGPU) has found its way into many fields as diverse as biology, linear algebra, cryptography, image processing, and so on, given the tremendous computational power provided by GPUs such as massive parallel threads and high memory bandwidth as compared to CPUs. In parallel to this trend, GPUs are increasingly leveraged to accelerate graph algorithms with either GPU-specific optimizations [18] or Pregel-like programming interfaces to hide the hardware intricacies [37], [7], [35], [29]. However, it is still challenging to design a GPU-based graph computing system that can exploit the hardware characteristics of GPUs efficiently, and provide a flexible user interface at the same time.

Existing graph processing systems mainly use the Compressed Sparse Row (CSR) representation of graphs due to its compact storage requirement. However, the low storage space consumption comes at a cost of non-coalesced access to GPU memory because of poor memory access locality. CuSha [7] is a graph processing framework that enables users to write vertex-centric algorithms on GPU, proposing a new graph representation called G-Shards to minimize non-coalesced memory accesses. However, this representation is not space efficient, which may exacerbate the situation when more GPU memory is needed to process large graphs. Medusa [37] is a general purpose GPU-based graph processing framework that provides high-level APIs for easy programming and scales to multiple GPUs. The achievable performance of Medusa may be limited by its internal data organization and processing logic that result in both irregular memory access and imbalanced workload distribution among GPU threads. [18] proposes techniques such as deferring outliers and dynamic workload distri-

Wenyong Zhong, Jianhua Sun, Hao Chen, Jun Xiao, Zhiwen Chen, Chang Cheng are with College of Computer Science and Electronic Engineering, Hunan University, Changsha, China. E-mail: {hnuzwy,jhsun,haochen}@hnu.edu.cn.

bution to alleviate intra-warp divergence and achieve a balanced load among different warps. However, the improvement in performance is limited because of its relatively heavyweight implementation.

In this paper, we present a general graph processing framework for GPUs, and our goal is to provide a simpler programming model without any performance loss and expressibility reduction. In particular, two novel algorithmic optimizations, lightweight approximate sorting and data layout transformation, are proposed to tackle the performance issues in existing frameworks. The approximate sorting can efficiently alleviate load imbalance on the GPU due to non-uniform degree distribution in graphs. The data layout transformation is effective in optimizing memory representation of key data structures to coalesce memory access. We believe that the proposed optimizations are not tightly-coupled to our system, and applicable to other similar frameworks.

The main contributions of this paper include:

- In order to exploit the fine-grained parallelism on GPUs, we present a general graph computing framework using a customized Edge-Vertex programming model instead of the traditional vertex-centric model. Compared with existing GPU-based frameworks such as Medusa that employs a more complex programming model, our system offers a simpler interface without the reduction of performance. We strike a balance between the programming simplicity and the exploitation of performance on GPUs.

- We recognize that load imbalance among GPU threads in existing graph processing systems has important implications on performance. So, we introduce an efficient approach called *approximate sorting* to address this issue, which greatly alleviates imbalance at minimal cost. In addition, we observe that key data structures in GPU-based graph systems may suffer from severe non-coalesced memory accesses, which significantly hinders scalability. Thus, we propose a lightweight algorithm to transform the original row-major layout to column-major layout to mitigates non-coalesced access patterns.

- We conduct extensive performance evaluations on a set of representative graph datasets that include both real world power-law graphs and synthesized random graphs, and the results indicate that our system outperforms an existing graph processing system.

# 2 BACKGROUND

In this section, we present the necessary background on the Pregel programming model and GPU architecture.

# 2.1 Pregel Programming Model

The Pregel programming model is inspired by the Bulk Synchronous Parallel model [34]. In this model, programmers express the parallelism of graph computation by a sequence of iterations called supersteps. During each superstep, the framework invokes an user-defined function for each vertex in parallel. Inside this function, the vertices receive its incoming messages from other vertices in the prior superstep, then the vertices update their values and send messages to other vertices that will be used in the next superstep [28]. Although simple, the Pregel programming model is flexible to express many graph algorithms.

Several variants of the Pregel programming model were also proposed such as some open-source implementations Hama [2], Giraph [1] and GPS [28], which target distributed environments. At the same time, efforts are devoted to extending the original Pregel model in order to optimize the performance for other parallel architectures. For example, Medusa [37] is an efficient implementation of applying the Pregel model to GPU platforms, with some distinguishable features to accommodate the inherent characteristics of GPUs.

Medusa provides a more fine-grained programming interface than Pregel, exposing fine-grained data parallelism on edges, vertices and messages, which is called EMV model. This model enhances the vertex-centric model to provide support for efficient graph processing on GPUs. Using the APIs offered by Medusa, programmers can define computations on vertices, edges and messages respectively. However, the EMV model is still complicated for programmers compared with the vertex-centric interface. Although Medusa processes edges, vertices, and messages separately with different GPU kernels to exploit GPU parallelism, load imbalance among GPU threads within warps/thread blocks still exists, leading to GPU resource underutilization.

Medusa proposes a graph-aware buffer scheme for the message buffer. In the EMV model, messages are usually sent or received along the edge. Therefore, an edge can send one or more messages to the message buffer. The size of the message buffer is pre-defined according to the number of edges in the graph and the maximum messages that an edge will send. The locations to store messages on GPU are established on CPU by constructing a reverse graph. As a result, the write positions of messages sent to the same vertex are consecutive. However, when vertices read messages from the message buffer, the threads in a warp would read the randomly scattered messages in the global memory, violating the requirement of coalesced memory access.

## 2.2 GPU and CUDA Programming Framework

The current generation of GPUs have thousands of processing cores that can be used for general-purpose computing. For example, the Kepler GPU GTX780 consists of 12 Streaming Multiprocessors (SMXs), each equipped with up to 192 Stream Processors (SPs). Each SMX has 64 KB of onchip memory that can be configured as 48 KB of shared memory with 16 KB of L1 cache, or as 16 KB of shared memory with 48 KB of L1 cache, and 1536 KB L2 cache is shared by all SMXs. In addition to the L1 cache, Kepler introduces a 48 KB read-only data cache. Each SMX has 64 KB 32bit registers equally split to the threads running in one block. In contrast, the off-chip global memory has a much larger size (typically in GB range) and longer access latency.

The schedulable execution unit on the GPU is called a *warp* formed by a group of 32 threads. Warps are grouped together into *cooperative thread arrays* (CTAs), which are correspondingly structured as a *grid*. Typically, the threads

in a warp follow the same execution path and operate on distinct data in SIMT (Single Instruction Multiple Threads) fashion in order to achieve maximal parallelism. Warp divergence may occur when there are conditional branches taken on the execution path. Launching a large number of threads concurrently is a recommended way to hide the latency of global memory access and to better utilize the computational resources on the GPU.

CUDA (Compute Unified Device Architecture) is a GPGPU programming framework from NVIDIA. CUDA supports various memory spaces, such as register, constant, local, parameter, texture, shared, and global memory, which differ in size, addressability, access speed and access permissions. Perhaps the single most important performance consideration in programming for GPU architectures is the coalesced access to the global memory [5].

# **3** System Design

Our system is composed of two major parts: the Pregel-like high-level programming interface and the customized runtime for the GPU. The programming interface can simplify the programming task of using GPUs for graph computation. The runtime system can hide GPU hardware intricacies and specific optimizations. In this section, we first explain why existing graph computing models are not sufficient and propose the Edge-Vertex model. Then, we describe the workflow and APIs of our system. At last, we analyze the potential performance bottleneck of the proposed computing model.

# 3.1 Edge-Vertex Model

First, we describe the reason why the vertex-centric model can not fit in the GPU architecture directly. In the vertexcentric model, the developer needs to define a function (e.g., *compute*) to perform computations on individual vertices (such as sending or receiving messages along edges). In order to fully utilize the computational resource of GPUs, we need to map the function to each GPU thread to exploit the fine-grained parallelism of GPUs. However, real world graphs often exhibit power-law degree distribution, which indicates that the workload assigned to each GPU thread may be imbalanced, leading to suboptimal performance. To address this issue, the EMV model proposed in Medusa splits the computation into multiple components, separating the processing of vertex, edge, and message to offer the developer more flexibility in designing algorithmic optimizations. However, this benefit comes at the cost of incurring programming complexity such as exposing the structure of the message buffer to allow explicit management of messages. However, the expressibility of defining GPU-based computation on vertices and edges would be sufficient for most graph algorithms. Further, encapsulating the message buffer in the runtime system can not only reduce programming complexity but also provide the opportunity of implementing optimizations for different GPU hardware architectures.

Therefore, we partition the computation in the vertexcentric model into two methods such as *EdgeCompute* and *VertexCompute*, which we call the Edge-Vertex model. It is based on the consideration that in our model edges are responsible for sending messages to the message buffer and vertices conduct the real computation with the messages received from the buffer. In other words, how the message buffer is constructed and managed is invisible to the end user, striking a balance between the flexibility in optimizing certain graph algorithms and the complexity in writing graph applications. Furthermore, this simplification does not necessarily imply performance reduction because specifically designed optimizations can greatly improve the overall performance as will be shown in this paper.

# 3.2 Workflow and APIs

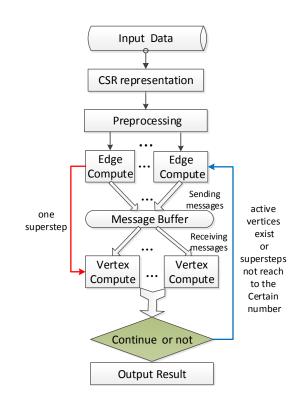

Figure 1 illustrates the workflow of our system. At first, the runtime system constructs the CSR representation [17] for the input graph data, and common management tasks including memory allocation on the CPU and GPU and data transfer between the host memory and GPU are also automatically fulfilled by the runtime system.

Fig. 1: The workflow of our system

# 3.2.1 Preprocessing

In our system, the preprocessing stage is managed by the runtime and is transparent to users. The internal message management module is an array-based buffer with associated operations of manipulating message delivery and reception. Before the actual graph processing, we first need to establish the accurate size for the chunked message buffer with each chunk representing the storage space for messages belonging to certain vertices. In particular, for a chunk of the message buffer that is assigned to a specific vertex, we need to calculate the positions where an edge can send messages to and a vertex can receive messages from in advance. The details will be given in section 4.2 when discussing the optimizations against the message buffering mechanism.

## 3.2.2 EdgeCompute stage

In the *EdgeCompute* stage, each GPU thread is responsible for one or more edges associated with a vertex and performs the operations of the following steps in order. First, the value and state of the source vertex are read. Second, the weight of the edge is obtained. Third, messages are delivered to destination vertices based on the results evaluated based on the vertex value and edge weight. Like the vertex-centric model, the state of each vertex is active at start, and the programmer can determine whether to vote to halt or not explicitly according to the algorithm's semantics.

## 3.2.3 VertexCompute stage

In the *VertexCompute* stage, one or more vertices are assigned to a GPU thread that takes the following three steps similar to the *EdgeCompute* stage. First, messages sent to the vertex are retrieved from the message buffer by the GPU thread. Second, the newly-obtained messages are used to compute the values for the vertex and its outgoing edges. Third, new state or value can be set to the vertex if needed. The invocation of the functions *EdgeCompute* and *VertexCompute* proceeds as a sequence of iterations until no active vertex exists or the pre-defined maximum number of supersteps are reached.

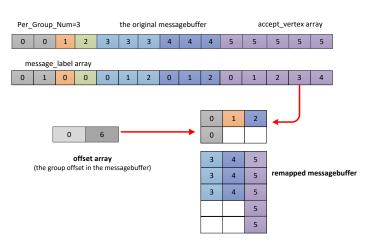

## 3.2.4 Message buffer

The message buffer is organized based on the total number of messages and the maximum number of messages each vertex can receive. Each edge is assigned a unique ID that is used as the index into the message buffer for both the stages. The ID values for the in-edges of a destination vertex are consecutive, which guarantees that messages sent to the same vertex are located contiguously in memory. Thus, the combiner in the VertexCompute stage can process the messages using a simple loop. This design together with the layout remapping discussed in Section 4.2 can greatly improve the overall performance.

# 3.2.5 Pregel-style API

In each superstep, each edge and vertex invoke the *Edge*-*Compute* and *VertexCompute* method provided by the user until certain conditions are met. The APIs we provide are shown in Table 1 with brief descriptions. Similar to existing frameworks, we divide the API into two categories: the userimplemented APIs and the system-provided APIs.

As for the user-implemented APIs, *initData* must be called to initialize data and configure parameters for threads and blocks on the GPU. As discussed earlier, programmers can define the computation with two separate functions *EdgeCompute* and *VertexCompute*. System-provided APIs are used as library calls to hide the GPU-specific programming details. Our system offers the method *startGPU* to invoke the device code, which in turn calls the corresponding user-defined functions. Two versions of *startGPU* are provided to control the iteration in different ways. One can be invoked with an explicit parameter setting the maximum supersteps,

TABLE 1: Pregel-style APIs

4

| user-implemented APIs                                            |

|------------------------------------------------------------------|

| /* EdgeCompute function, processing one edge. */                 |

| void EdgeCompute(Edge e);                                        |

| /* VertexCompute function, processing one vertex. */             |

| void VertexCompute(Vertex v);                                    |

| /* Initialize the value of edges and vertices, configure the     |

| number of threads and blocks on GPUs. */                         |

| void initData(void* graph,void* initalValues);                   |

| system-provided APIs                                             |

| /* Start the runtime system, and stop until reaching max-        |

| Supersteps specified by the programmer. */                       |

| void startGPU(int maxSupersteps);                                |

| /* Start the runtime system, and stop until no active            |

| vertices exist. */                                               |

| void startGPU();                                                 |

| /* Set the state of the vertex to inactive. */                   |

| void voteToHalt(Vertex v);                                       |

| /* Set the state of the vertex to active. */                     |

| voteToActive(Vertex v);                                          |

| /* Set the parameter continue to true, if there are still active |

| vertices sending messages in the next superstep. */              |

| void stillContinueNextSupersteps(bool continue);                 |

| /* Combine the incoming messages sent to the same                |

| vertex. */                                                       |

| Message Combiner(Vertex v);                                      |

|                                                                  |

and the other can determine the completion of computation by checking whether there will be active vertex in the next superstep.

# 3.2.6 A Running Example

In graph algorithms, finding the single source shortest paths (SSSP) in a graph is a well-known and easy-to-understand graph algorithm [12]. For this graph algorithm, we need to specify a vertex as the single source vertex and find a shortest path between the source vertex and every other vertex in the graph. We use a running example to illustrate how the three major functions *EdgeCompute,VertexCompute,* and *Combiner* are defined to implement the SSSP algorithm in our system. Algorithm 1 shows the expressibility and simplicity of the Edge-Vertex model in writing graph algorithms for GPUs.

The SSSP procedure works as follows. In each iteration, we first get the source node of each edge, and send messages to sink nodes if the source node is updated in the previous iteration. Then, in the vertex compute stage, the minimum value is calculated by scanning a segment of the message buffer that belongs to the current vertex. If it is less than the value from the previous iteration, the old value is updated with the new one, and the vertex votes to continue to the next step. Otherwise, the vertex deactivates itself by voting to halt. The whole procedure terminates when all vertices are simultaneously inactive.

# 3.3 Performance Bottleneck Analysis

Although our Edge-Vertex model can guarantee a balanced load distribution among GPU threads in the *EdgeCompute* stage because of the coalesced memory access ensured by the predetermined write positions, load imbalance still exists in the *VertexCompute* stage. For example, in the *VertexCompute* method of the SSSP algorithm, we need to combine messages belonging to a vertex. But the number of messages that a vertex receives may vary significantly due

5

| Algorithm | <b>1</b> T | he pseud | o code of | the SSSP | algorithm |

|-----------|------------|----------|-----------|----------|-----------|

|           |            | ·        |           |          |           |

| <pre>void EdgeCompute(Edge e) 1: Vertex srcVertex=e.getSrcVertex();</pre> |

|---------------------------------------------------------------------------|

| 2: if <i>srcVertex.active</i> then                                        |

| <ol> <li>e.sendMsg(srcVertex.value+e.weight);</li> </ol>                  |

| 4: end if                                                                 |

|                                                                           |

| void VertexCompute(Vertex v)                                              |

| 1: msg_min=Combiner(v);                                                   |

| 2: if $msg\_min < v.value$ then                                           |

| 3: vertex.value=msg_min;                                                  |

| 4: voteToActive(v);                                                       |

| <ol> <li>stillContinueNextSuperstep(true);</li> </ol>                     |

| 6: <b>else</b>                                                            |

| 7: $voteToHalt(v);$                                                       |

| 8: end if                                                                 |

| tunnel G. Managara int                                                    |

| typedef: Message int                                                      |

| Message <b>Combiner</b> (Vertex v)                                        |

| 1: min=INF;                                                               |

| 2: for each $i \in v.inEdgesNum$ do                                       |

| 3: if $min > v.currentMsg()$ then                                         |

| 4: min=v.currentMsg();                                                    |

| 5: end if                                                                 |

| 6: v.nextMsg();<br>7: end for                                             |

|                                                                           |

| 8: return min;                                                            |

to highly variable distribution of vertex degree in a graph, which causes not only divergence within a warp but also resource underutilization among blocks. In section 4.1, we propose a lightweight but effective optimization mechanism to address this issue.

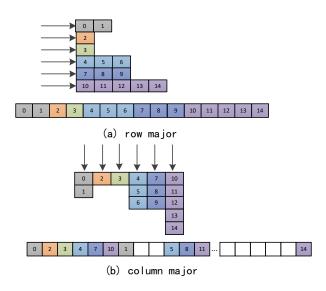

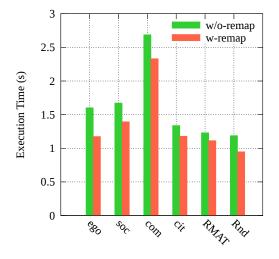

Another potential performance bottleneck comes from the *Combiner* method where each GPU thread reads messages from the message buffer in a non-coalesced way, because the message buffer is initialized on the CPU that favors a row-major memory layout and transfered to the GPU with the memory structure unchanged. But on the GPU we are often recommended to use a column oriented layout for data structures to fit in with the practice of GPU memory access optimization. However, it is difficult to arrange the message buffer in a way that works well for both cases. Thus, we will present another lightweight solution to optimize memory layout in section 4.2.

# 4 **OPTIMIZATIONS**

In this section, we present two novel optimizations to improve the performance of the runtime system. As stated earlier, we assume the CSR representation for the graph on the GPU.

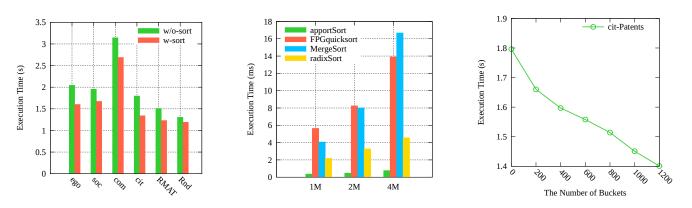

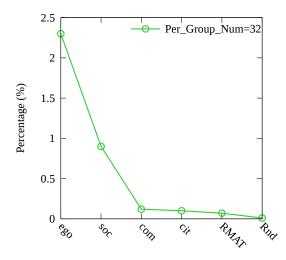

# 4.1 Optimizing Load Imbalance with Approximate Sort

Inherent irregularity in some applications may cause imbalanced workload distribution among GPU threads, resulting in ineffective utilization of compute resource. In our case, each vertex must receive incoming messages from the message buffer, while the maximum size of incoming messages for a vertex is determined by the in-degree of the vertex. As the in-degree distribution of a graph varies greatly, processing vertices with high variance of incoming messages in a warp or thread block will lead to workload imbalance. For example, a single thread in a warp processing comparatively large incoming messages for the vertex would introduce wasted resource as every vertex will take as many cycles as the largest one to process in the warp.

*implications:* Because current GPUs provide no support for fine-grained thread-level task scheduling, tackling the inefficiency incurred by workload irregularity imposes the responsibility of fine-tuning the algorithm on developers. An ideal solution to this problem should work well for a wide range of workloads. For example, it should achieve highest possible performance for highly irregular workloads, and at the same time guarantee lowest possible cost for regular workloads.

Approaches: To address this issue, one possible approach is to identify outliers in incoming messages to defer the processing of these messages to subsequent kernels [18]. For example, vertices with an excessive large/small number of incoming messages are delayed to process. However, this method incurs considerable overhead, so more lightweight solutions are preferred. Although existing work [31] indicates that it is not worthwhile to group packets with identical or similar size by GPU sorting algorithms when accelerating the network stream processing with GPUs. However, we found that pre-sorting the message buffer according to the vertex in-degree on the CPU can result in a significant performance increase for the vertex kernel. Moreover, balancing the workload within warps or thread blocks does not necessarily require a strict ordering. These investigations are the direct motivation of designing a GPUbased approximate sorting algorithm for our system as detailed below.

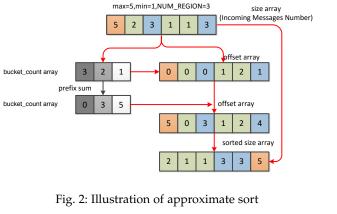

Before discussing the details of the approximate sorting, we first present a high-level overview about this algorithm. Conceptually, the approximate sorting maps elements to different buckets with a linear projection, and the ordering among buckets is guaranteed (all the elements in a bucket must be larger or smaller than those in its consecutive bucket). However, we do not maintain ordering in buckets (elements in a bucket are unordered, but the elements are similar in size). In comparison, traditional sorting algorithms require a precise ordering among all elements, which is not necessary for our purpose and incurs more overhead.

As shown in Figure 2, our algorithm operates in three steps. First, each element in the size array (calculated based on vertex in-degrees) is mapped into a bucket (the number of buckets is a pre-defined parameter and typically much less than the array size). In this step, we maintain an ordering among all elements that are mapped into the same buckets and a counter array that records the size of each bucket. Second, an exclusive prefix sum operation is performed on the counter array. In the third step, the results of the above two steps are combined to produce the final coordinates that are then used to transform the input vector to an approximately-sorted form.

**Step 1:** Similar to many parallel sort algorithms that subdivide the input into equally-sized buckets and then sort each bucket in parallel, we first map each element of the size

This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/TPDS.2016.2611659, IEEE Transactions on Parallel and Distributed Systems

| T * 4*  | A • •     |     |        |    | 1 1 /    |

|---------|-----------|-----|--------|----|----------|

| Listing | Assigning | ele | ements | to | buckets. |

|         |           |     |        |    |          |

| 1global void assign_bucket(uint *input,uint lenght,uint max,uint min,<br>2 uint *offset,uint *bucket_count,uint *bucket_index) |

|--------------------------------------------------------------------------------------------------------------------------------|

| 3 {                                                                                                                            |

| 4 int idx = threadx.x + blockDim.x * blockIdx.x;                                                                               |

| 5 uint bucket_idx;                                                                                                             |

| 6 <b>for</b> (; $idx < lenght$ ; $idx += total_threads$ )                                                                      |

| 7 {                                                                                                                            |

| 8 uint value=input[idx];                                                                                                       |

| 9                                                                                                                              |

| <pre>10 bucket_idx = (size - min)*(NUM_BUCKETS - 1)/(max - min);</pre>                                                         |

| <pre>11 bucket_index[idx] = bucket_idx;</pre>                                                                                  |

| 12                                                                                                                             |

| <pre>13 offset[idx] = atomicInc(&amp;bucket_count[bucket_idx], length);</pre>                                                  |

| 14 }                                                                                                                           |

| 15 }                                                                                                                           |

| ,                                                                                                                              |

array into a bucket. As shown in Listing 1, the number of buckets is a fixed value NUM\_BUCKETS, and the mapping procedure is a linear projection of each element in the input vector to one of the NUM\_BUCKETS buckets. The linear projection is demonstrated at lines 10 and 11 in Listing 1, where the variables of *min* and *max* represent the minimum and maximum value in the input respectively, which can be obtained efficiently on GPUs. In this way, each bucket represents a partition of the interval [min, max], and all buckets have the same width of  $\frac{max-min}{NUM_BUCKETS}$ . The elements in the input vector are assigned to the target bucket whose value range contains the corresponding element. In addition, another *count array* is maintained to record the number of elements assigned to each bucket. As shown at line 13, the counting is based on an atomic function provided by CUDA, atomicInc, to avoid the potential conflicts incurred by concurrent writes. The function atomicInc returns the old value located at the address presented by its first parameter, which can be leveraged to indicate the local ordering among all the elements assigned to the same bucket. The Kepler GPUs has substantially improved the throughput of global memory atomic operations as compared to Fermi GPUs, which also has been observed in our implementation.

**Step 2:** Having obtained the counters for each bucket and the local ordering within a specific bucket, we perform a *prefix sum* operation on the counters to determine the address at which each bucket's data would start. Given an input array, the prefix sum, also known as scan, is to generate a new array in which each element *i* is the sum of all elements up to and including/excluding *i* (corresponding to inclusive and exclusive *prefix sum* respectively). Because

| Listing 2: the key step of approximate sort.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1global void appr_sort(uint *key,uint *key_sorted,void *value,uint length,         2       void *value_sorted,uint *offset,uint *bucket_count,         3       uint *bucket_index,uint *oldToNew)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| $4 \left\{ \frac{1}{2} + \frac{1}{2} +$ |

| 5 int idx = threadIdx.x + blockDim.x * blockIdx.x;<br>6 uint count = 0;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 6 <b>unt</b> count = 0;<br>7 <b>for</b> (; idx $\leq$ length; idx $+=$ total_threads)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 8 {                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| <pre>9 uint key = key[idx];</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 10 uint value = value[idx];                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 12 uint bucket_index = bucket_index[idx];                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| <pre>13 count = backet_count[bucket_index];</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 14 <b>uint</b> off = offset[idx];                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 15 off = off + count;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

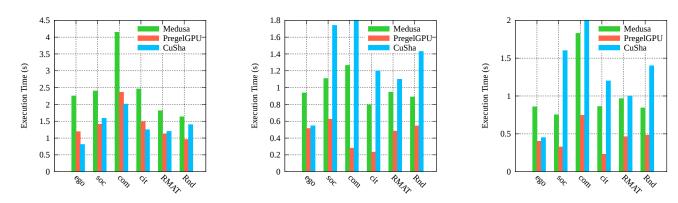

| <pre>17 key_sorted[off] = key;</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |